# VMSL: A Separation Logic for Mechanised Robust Safety of Virtual Machines Communicating above FF-A

ZONGYUAN LIU, SERGEI STEPANENKO, JEAN PICHON-PHARABOD, AMIN TIMANY, ASLAN ASKAROV, and LARS BIRKEDAL, Aarhus University, Denmark

Thin hypervisors make it possible to isolate key security components like keychains, fingerprint readers, and digital wallets from the easily-compromised operating system. To work together, virtual machines running on top of the hypervisor can make hypercalls to the hypervisor to share pages between each other in a controlled way. However, the design of such hypercall ABIs remains a delicate balancing task between conflicting needs for expressivity, performance, and security. In particular, it raises the question of what makes the specification of a hypervisor, and of its hypercall ABIs, good enough for the virtual machines. In this paper, we validate the expressivity and security of the design of the hypercall ABIs of Arm's FF-A. We formalise a substantial fragment of FF-A as a machine with a simplified ISA in which hypercalls are steps of the machine. We then develop VMSL, a novel separation logic, which we prove sound with respect to the machine execution model, and use it to reason modularly about virtual machines which communicate through the hypercall ABIs, demonstrating the hypercall ABIs' expressivity. Moreover, we use the logic to prove *robust safety* of communicating virtual machines, that is, the guarantee that even if some of the virtual machines are compromised and execute unknown code, they cannot break the safety properties of other virtual machines running known code. This demonstrates the intended security guarantees of the hypercall ABIs. All the results in the paper have been formalised in Coq using the Iris framework.

CCS Concepts: • Theory of computation  $\rightarrow$  Separation logic; Program verification; • Security and privacy  $\rightarrow$  Virtualization and security; Logic and verification.

Additional Key Words and Phrases: hypercall, FF-A, robust safety, separation logic, logical relation, Iris

#### **ACM Reference Format:**

Zongyuan Liu, Sergei Stepanenko, Jean Pichon-Pharabod, Amin Timany, Aslan Askarov, and Lars Birkedal. 2023. VMSL: A Separation Logic for Mechanised Robust Safety of Virtual Machines Communicating above FF-A. *Proc. ACM Program. Lang.* 7, PLDI, Article 165 (June 2023), 25 pages. https://doi.org/10.1145/3591279

## 1 INTRODUCTION

A verification effort can only ever be as good as the specification it relies on. This is especially true for key security components like hypervisors, where a single error in design can void all security guarantees. Specifications for real-world programs are sizeable programs themselves, and thus commonly suffer from bugs themselves; and while some are found during the verification effort [Nienhuis et al. 2020, §VI], this is not always the case [Chidambaram 2018]. Moreover, the verification effort does not necessarily validate the expressivity of the specification either. To address this, specifications themselves need to be validated and tested, in particular by exercising them to verify client code. In the terminology of DeepSpec, we need to make sure that specifications

Authors' address: Zongyuan Liu, zy.liu@cs.au.dk; Sergei Stepanenko, sergei.stepanenko@cs.au.dk; Jean Pichon-Pharabod, jean.pichon@cs.au.dk; Amin Timany, timany@cs.au.dk; Aslan Askarov, aslan@cs.au.dk; Lars Birkedal, birkedal@cs.au.dk, Aarhus University, Aarhus, Denmark.

This work is licensed under a Creative Commons Attribution 4.0 International License.

© 2023 Copyright held by the owner/author(s).

2475-1421/2023/6-ART165

https://doi.org/10.1145/3591279

are 'live' [Appel et al. 2017], in that they are "connected via machine-checkable proofs to [not just] the implementation [but also to] client code".

In this paper, we formalise and validate a substantial fragment of the hypercall (aka 'hypervisor call', HVC) ABIs of FF-A, the Arm Firmware Framework for Arm A-profile [Arm Ltd. 2022], as implemented by Google's Hafnium hypervisor [Hafnium development team 2022]. The hypercall ABIs allow virtual machines (VMs) running atop of a hypervisor to communicate and share data, e.g., by sending messages or by controlled sharing of memory pages, and to pass control to others. Our formalisation simplifies the ABIs compared to the informal FF-A specifications, but still captures the essence (see Section 2.1 for details). We then validate it by exercising it to verify key scenarios of VMs using the ABIs for controlled sharing of memory in the presence of adversarial, unknown code. Controlled sharing is essential for communication between VMs in real use cases, but makes the security analysis of hypervisors much more challenging.

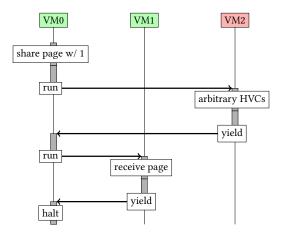

Our running example is that of Figure 1, where the 'primary' VM (typically, Linux) is privileged, and can ask the hypervisor to schedule other, 'secondary' VMs (typically, the keychain, or DRMs). Here, we have two secondary VMs: one running known code, VM1, and one adversarial, running unknown code, VM2; each VM has its own pages, disjoint from those of the others. The primary VM, VM0, first asks the hypervisor to share one of its pages with VM1; then asks the hypervisor to run the adversarial VM2; and, when given back control, asks the hypervisor to run the known VM1.

Dealing with the HVC ABIs and their underlying use of virtual memory adds many components to the machine state: page tables, in-flight memory sharing transactions between VMs, etc. Managing the size and details of such a machine state poses a significant proof engineering challenge. For reasoning to be tractable, we need to be able to reason about known VMs individually: we should only need to consider the relevant parts of the machine state, and only need to take interference into account at interaction points, not at every step of the program.

To this end, we develop VMSL, a novel higher-order separation logic that supports formal modular reasoning about the execution of communicating VMs. VMSL effectively reduces the problem of verifying VMs communicating via the hypercall ABIs of FF-A to well-studied problems: cooperative multitasking, and functional correctness of assembly.

One key intuitive desired security guarantee is *robust safety*: no matter what HVCs the adversarial VM2 may invoke, it will not be able to affect the private pages of VM0 and VM1, nor the page shared between only VM0 and VM1. This requires carefully designed ABIs, posing constraints to each HVC, making sure the desired guarantee is not breakable in any case, which results in a sophisticated and lengthy informal FF-A specification [Arm Ltd. 2022]. In this paper, we describe how to capture robust safety formally, even in the presence of in-flight transactions between VMs, and how to prove that the ABI specifications enforce robust safety.

We highlight the following features of our VMSL logic:

- VMSL is foundational [Appel 2001]: we mechanise the definition of VMSL and prove it sound in Coq using the Iris separation logic framework [Jung et al. 2018] and the Iris Proof Mode [Krebbers et al. 2017]. Both the definition of VMSL and the examples using VMSL extensively rely on the expressive power of Iris to make reasoning about low-level code tractable, and we point out where we utilise it throughout the paper.

- VMSL supports modular reasoning in the sense that each VM can be verified individually. This is crucial for formal verification to work at scale.

- VMSL features two compatible logical resource sharing mechanisms to support reasoning about communication between VMs: (1) standard separation logic invariants, and (2) our *resumption conditions*, a logical sharing mechanism that offers more convenience than standard invariants for communication between VMs in the style of cooperative multitasking.

Fig. 1. A motivating example where a compromised VM2 is contained: the page sharing between VM0 and VM1 is guaranteed to succeed if the adversarial VM2 yields, no matter what other HVCs VM2 makes. The memory integrity of the page is guaranteed.

- VMSL is factored in two parts: a general part that handles issues that arise for any low-level model with scheduling, and a specific part that deals with the HVC ABIs of FF-A.

- VMSL is sufficiently expressive to support not only formal reasoning about concrete known programs, but also the definition of so-called logical relations which can be used to reason about robust safety. We use logical relations to reason about scenarios like that of Figure 1, where some VMs run known code and others run unknown possibly adversarial code.

## Contributions.

- We formalise a substantial fragment of the Arm's FF-A ABIs, as implemented by Hafnium, in the form of an operational semantics in which HVCs are primitive steps (Section 2).

- We develop and prove soundness of VMSL, a novel separation logic for modular reasoning about communicating VMs (Section 3).

- We show how we capture the desired security guarantees using logical relations, and how we apply them to reason about robust safety (Section 4).

All of our results are mechanised in Coq using Iris. The Coq formalisation and the instructions of usage are available in the supplementary material [Liu et al. 2023].

Non-goals. We focus on exercising the HVC ABIs, and thus do not address other key complementary aspects, which we discuss in Section 5. In particular: (1) We are not verifying a hypervisor, but rather making sure that the hypervisor specification that we are providing is adequate. (2) We focus on the HVC ABIs, and our operational semantics is a minimalistic instruction set: it has the right shape, but it is far from a full-scale ISA. (3) Our operational semantics does not include interrupts, and assumes that there is no concurrency, as characterising the semantics of virtual memory in a concurrent setting is work in progress [Simner et al. 2022].

Threat model. We only consider integrity, not secrecy. Our attacker model is that of adversary VMs running unknown code; we do not consider side-channels. To reason about adversarial VMs running unknown code, we only assume knowledge of initially accessible pages and transactions related to adversaries; both the content of memory and registers of adversaries are unspecified. Adversaries therefore could perform attacks by executing malicious code stored in their memory. For instance,

adversaries could invoke arbitrary HVCs to try to interfere with in-flight transactions between trusted VMs, or read/write memory of other VMs. With this model, we show that adversaries cannot break the integrity of memory under protection of hardware and the hypervisor.

## 2 FORMALISING A SUBSTANTIAL FRAGMENT OF THE HVC ABIS

As we focus on the HVC ABIs, we use a simplified subset of the Arm-A instruction set, with only one unusual feature: the hvc instruction. Figure 2 shows the running example of Figure 1 more precisely in our language.

## 2.1 Scope

We specify the hardware behaviours of virtualisation, including page table lookup and context switching, plus the following HVCs of FF-A: (1) for memory sharing: Donate, Lend, Share, Retrieve, Relinquish, and Reclaim; (2) for scheduling: Run, Yield, and Wait; and (3) for messaging: (asynchronous) Send and Poll. This covers most of FF-A, apart of the 'secure world' trusted computing functionality involving TrustZone. We omit the synchronous variant of Send, which requires extra machinery without increasing expressivity, and the new messaging HVC, notify, that was introduced after this work started.

Simplification. We make two main simplifications in our model of FF-A: (1) We only formalise the ownership and access fields of the page table entries, and only consider read-write permissions. (2) We only model 1-to-1 sharing (as implemented by Hafnium) instead of 1-to-n, and accordingly simplify the format of transaction descriptors. These, along with other minor simplifications, help keep the size of our model manageable, but do not significantly omit specification details or impact expressivity. For instance, we believe the model can be adapted to support 1-to-n sharing.

Conformance. As with any formal modeling activity, there is an unavoidable gap between the informal FF-A specification and our formal specification. We have tried to follow the intent of the informal specification when designing our formal model, and cross-referenced it with the Hafnium implementation of the informal spec to gain more confidence in our formal model. Future work includes showing that some of the Hafnium HVC implementations *refine* our formal model.

# 2.2 Formalising HVCs

Informally, a hypervisor provides the illusion to VMs that they are running on a machine in which the whole HVC is just a step of the machine; the hypervisor itself is invisible. Accordingly, in our model, an HVC is a primitive step of the operational semantics. The reduction rule for a Share in Figure 3 is a representative example, and we explain it below.

2.2.1 Memory Access. On a concrete machine, an hvc causes a jump to a higher exception level and the execution of hypervisor code. The hypervisor code operates on its private data in physical memory; in our model, the private state of the hypervisor is represented abstractly, separate from the physical memory that the VMs operate on, which we model as a partial function from memory addresses to machine words (both are represented by our type of machine words, Word).

In particular, on a concrete machine, the page tables are in-memory data structures that are edited by the hypervisor and looked up by the hardware; in our model, the page tables are merged into one partial (mathematical) function that is updated by memory-sharing HVCs. The partial function maps a page identifier (page base address, which is sufficient, given that we assume identity address mappings) to a *page status*, which is composed of an optional page owner, the set of *VMIDs* of the VMs that have access to the page, and a bit indicating whether it is exclusively owned (can only be accessed) by one VM. For instance, the status of page *p* in the example of

Fig. 2. Code of the two known VMs in Figure 1. Additional notation is added to improve readablity. Symbols with prefix # are constant values: x is the data stored in R0 that VM0 will share with VM1; p is the page that VM0 will share (represented with the base address of the page); ptx is the base addresses of the write-only messaging buffer (TX) of VM0, and prx is the read-only buffer (RX) of VM1. We assume that the two programs live at the start of two separate pages,  $pp_0$  and  $pp_1$ .

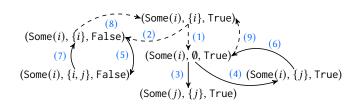

Figure 2 is initially (Some(0),  $\{0\}$ , True), since VM0 has exclusive ownership on the page; and it is updated to (Some(0),  $\{0,1\}$ , False) after the page is shared with VM1.

When a VM with VMID i tries to perform a memory access at an address a, e.g. str at line 4 storing the value in R5 to address p, the page status of the page p is looked up in the page table, and checked to determine whether the VM is allowed to access p (which it can in this case, since 0 is an element of the 'accessible' set  $\{0\}$ ). If the access is not allowed by the page table, a page fault is raised. In our setup, this terminates the execution (of all VMs, because there is no concurrency) with the execution mode PageFault, and therefore a page fault is safe.

2.2.2 Configuration. A configuration is a pair of a state together with an execution mode. A state of our operational semantics is composed of the aforementioned components for modeling memory access, plus those for HVCs:

```

State \stackrel{\mathrm{def}}{=} \left\{ \begin{array}{ll} \textit{mem} & : \textit{Word} \rightarrow \textit{Word}; & \textit{pgt} & : \textit{PageID} \rightarrow \textit{PageStatus}; \\ \textit{regs} & : \textit{VMID} \rightarrow \textit{RegisterFile}; & \textit{curr} & : \textit{VMID}; \\ \textit{trans} & : \textit{Transactions}; & \textit{mb} & : \textit{VMID} \rightarrow \textit{Mailbox}; \end{array} \right.

```

We have three execution modes: Normal, PageFault, and Halted.

The machine can only take a further step to execute the next instruction if it is in Normal mode. Halted is the mode reached by 'normal' termination via the halt instruction, and, as stated above, PageFault is used for page faults.

2.2.3 Transactions. On a concrete machine, to support memory sharing transactions between VMs, the hypervisor needs to maintain some metadata in its private memory; in our model, we keep a partial mapping from transaction handles (machine words) to abstract *transactions*, which are composed of the sender, the receiver, the set of pages being sent, the type of the transaction, and the state of it (a bit indicating whether the receiver has retrieved the access to the pages). For instance, the hvc at line 13 of VM0 invokes a sharing transaction of page p to VM1, which is represented as  $Some((0, 1, \{p\}, Share), False)$  (see the last line of antecedents in the rule in Figure 3).

A VM is allowed to send pages to other VMs via transactions. To do so, the sending VM first has to prepare a transaction descriptor specifying the receiver and the page IDs of the pages in its TX page (lines 5–9 in the example). Next, the sending VM invokes a memory sending HVC, asking the hypervisor to create a transaction of the type given by the descriptor. The type of transaction (donation, sharing, or lending) determines the effect of the HVC on the status of the pages being sent, as per Figure 4. The sharing of page p in the example corresponds to edges (2)

Fig. 3. Reduction rule for Share

Fig. 4. The state transition system of the status of a page during a transaction. HVCs with dashed arrows are allowed for the sender i, and others are allowed for the receiver j. (1) Donate/Lend (2) Share (3) Retrieve(donation) (4) Retrieve(lending) (5) Retrieve(sharing) (6)(7) Relinquish (8)(9) Reclaim

and (5). In all cases, the hypervisor checks that the pages are owned and exclusively accessible by the sender before creating the transaction (e.g. done by  $valid\_share$  in Figure 3). If the checking fails, the hypervisor returns an error code to the VM and resumes its execution. If it succeeds, the hypervisor then returns a fresh handle h (initially mapped to None, meaning that it is not bound to any transaction) referring to the newly created transaction to the sender, and remembers the transaction in its metadata (trans).

VMs can invoke other HVCs with the same handle to refer to the transaction. For instance, with the hvc at line 10, VM1 Retrieves access to the page, flipping the retrieved bit to True. In case of donation, this HVC also transfers ownership of the pages to the receiver and finishes the transaction (and frees the handle). In case of sharing or lending, the receiver could Relinquish access to the pages afterwards, flipping the bit back. The sender can Reclaim exclusive access to the pages if the access has not been retrieved, or has been relinquished by the receiver (in either case, the retrieved bit is False), which is the second way of ending the transaction.

2.2.4 Scheduling. On a concrete machine, to support switching between VMs, the hypervisor needs to save registers by spilling them in its private memory, and restore them upon context switching; in our model, we keep a total mapping (regs) from VMIDs to register files, where a register file is itself a map from register names to words, and a VMID (curr) to remember which VM is currently running.

By duplicating *RegisterFile* and picking the right one to update according to *curr* when registers are modified, we avoid modelling register saving and restoring at context switching. For instance, mov at line 3 of VM0 only updates R5 of VM0 since *curr* is 0. As a consequence, the switching HVCs only need to change *curr*.

FF-A allows putting the responsibility of scheduling VMs either on the hypervisor, or delegates it to VM0, the 'primary' VM. Typically, thin hypervisors like Hafnium choose the latter, for instance letting the thread scheduler of Linux make scheduling decisions. We model the latter use case.

Therefore, it grants the primary VM the privilege to Run other so-called secondary VMs. Secondary VMs are only allowed to return control back to the primary; either explicitly with Yield, or as the consequence of an HVC, for example to wait for a message with Wait.

2.2.5 Messaging. To support messaging between VMs, on a concrete machine, the hypervisor needs to maintain two dedicated memory pages, named TX and RX, as the message buffers for each VM, and remembering the state of all RX buffers (e.g. whether the buffer is full); in our model, we keep a total mapping (mb) from VMID to Mailbox, which consists of two buffers.

The TX and RX buffers are respectively write-only and read-only, and are used for sending and receiving messages between two VMs, or a VM and the hypervisor. Line 21 of VM0 Sends the handle referring to the sharing transaction to VM1. The hypervisor copies the handle from the TX page of VM0, pastes it to the RX page of VM1, and remembers the length and the sender in its private state as Some(1,0). In the case where the sender is a secondary VM, the control is yielded to the primary immediately, notifying it that a message has just been sent to the receiver, so that the primary can schedule the receiver to run next to actually receive the message. The receiver, like VM1, can ask for the length and the sender of the message with Poll (line 6 of VM1), which also notifies the hypervisor that it is ready to take the next message (updates the RX buffer to None).

2.2.6 Calling Convention. The calling convention that we have used in the example above works in general as follows: to invoke a specific HVC, a VM executes the hvc instruction with the identifier of the HVC in R0, and other arguments saved in successive general-purpose registers (for example, the identifier of the VM to Run in R1), or in the TX buffer (for "large" arguments like transaction descriptors), as appropriate. Return values, including whether the HVC is successful and possible error codes, are passed back to the VM via return registers, like in Figure 3, or RX buffers (depending on the HVC).

#### 3 REASONING ABOUT COMMUNICATING VMS

To validate our model of the FF-A HVC ABIs, we develop VMSL, a program logic designed to reason about key scenarios of VMs communicating using the FF-A ABIs. We start this section by discussing two of the key challenges involved in developing a program logic for communicating VMs.

The programs running on VMs are imperative and operate on mutable shared data and so we base VMSL on separation logic [Reynolds 2002]. In particular, this will allow us to support *local reasoning* via the *frame rule* of separation logic, as we show below.

The first challenge is that we wish to reason about a low-level language model where instructions are stored in the memory, which complicates the formulation of a sequential composition proof rule, which usually makes it possible to reason about instructions one at a time. This is a common problem, and we neatly capture a 'folklore' solution in a small Iris library in the form of *single-step weakest preconditions*. We discuss how our approach relates to previous work on program logics for assembly in Section 5.

The second key challenge is that we wish to support 'VM-local' reasoning: it should be possible to verify each VM individually. This is analogous to 'thread-local' reasoning in concurrent separation logic, and is crucial for formal verification to work at scale. We could treat each VM in a manner similar to how a thread is treated in concurrent separation logic, and then use concurrent separation logic style *invariants* to reason about sharing of data among different VMs. However, such invariants were designed for concurrency, and pose an undue burden in our setting where VMs are executed sequentially but not concurrently. Therefore, we introduce *resumption conditions*, an alternative

Fig. 5. The proof rule for an immediate-to-register mov instruction. The updated resources are highlighted as in later rules. For simplicity, we omit the *encode* function that maps non-words including instructions and HVC identifiers to *Words* in later rules. Also, we use IsInstr@i(s, a, mov r n) to represent that the mov instruction is stored at address a which belongs to the page that is one of VMi's accessible pages s ((1) to (4)).

mechanism to share resources among VMs, which allows a VM to use shared resources freely during its execution until control is transferred to another VM.

We explain our solutions to the two challenges on our example in Section 3.2; motivate and describe them in more detail in Section 3.3. With the solutions implemented in VMSL using Iris, we prove soundness of the logic with respect to the operational semantics of the machine model. All of VMSL's proof rules are sound with respect to our definition of weakest preconditions, and we have proven an *adequacy theorem* which intuitively says that if a weakest precondition holds in the VMSL, then it really means that it is safe to execute the program on the machine. We refer the reader to our Coq formalisation for a precise formal statement of the soundness and adequacy theorems and the proofs thereof.

## 3.1 VMSL

In this section we introduce VMSL by explaining how it is used to specify and reason about VMs executing *known* code. We use a simplified variant of Figure 2 without invoking the unknown VM2 (that is, with lines 22–25 of VM0 removed) as a running example.

- 3.1.1 Informal Specification. In this example, the primary VM writes the content x of register R0 to the first location of page p, shares the page with VM1, then schedules VM1. VM1 retrieves access to the page p, increments the first location of p by two, then yields. The primary VM then reads from p into R0, and halts. We want to show that it reads x + 2.

- 3.1.2 Points-to Assertions. To state this formally, we introduce the classic register 'points-to' assertion,  $r@i \xrightarrow{\text{reg}} v$ , which captures the fact that register r contains the value v; because our registers are banked, we specify which VM the register belongs to via its VMID, i. As usual in separation logic, our assertion also captures ownership of register r of VMID i, so that this assertion is exclusive. In Table 1, we present a collection of similar points-to predicates of VMSL, together with their intuitive meanings. We introduce most of them gradually along with our explanation of how we use VMSL to reason about the example.

- 3.1.3 Formal Specification. Returning to the example, starting from a state where  $R0@0 \xrightarrow{reg} x$ , with other resources and some side conditions we introduce below, we want to show that, when the machine terminates, VM0 reaches a Halted state (indicating success), and moreover we have  $R0@0 \xrightarrow{reg} x + 2$ . We phrase this in VMSL by using a *weakest precondition* predicate *WP m @ i {Q}* which expresses the partial correctness of the VM*i*, i.e., we execute the VM with mode *m* and, if it terminates, then the postcondition *Q* holds:

| Predicate                                                             | Intuition                                               |  |  |

|-----------------------------------------------------------------------|---------------------------------------------------------|--|--|

| $r@i \xrightarrow{\operatorname{reg}} w$                              | register <i>r</i> of VM <i>i</i> contains word <i>w</i> |  |  |

| $a \stackrel{\text{mem}}{\longmapsto} w$                              | value $w$ is at location $a$                            |  |  |

| $\operatorname{Pgt}@i \stackrel{\operatorname{acc}}{\longmapsto} s$   | VMi has access to pages s                               |  |  |

| $\operatorname{Pgt}@p \stackrel{\operatorname{own}}{\longmapsto} i$   | VMi owns page p                                         |  |  |

| $Pgt@p \overset{excl}{\longmapsto} i$                                 | VMi's access to page $p$ is exclusive                   |  |  |

| $\operatorname{Tran}@h \stackrel{\operatorname{tran}}{\longmapsto} t$ | transaction $t$ is bound to handle $h$                  |  |  |

| $\operatorname{Tran}@h \stackrel{\operatorname{rtrv}}{\longmapsto} b$ | status of transaction bound to $h$ is $b$               |  |  |

| $Mb@i \xrightarrow{rx} p$                                             | VMi's RX page is p                                      |  |  |

| $Mb@i \overset{tx}{\longmapsto} p$                                    | VMi's TX page is p                                      |  |  |

| MemPage(p, ws)                                                        | content of page <i>p</i> is ws                          |  |  |

| FreshHandles(hs)                                                      | handles hs are fresh                                    |  |  |

Table 1. Selected collection of resources of VMSL

$$\mathsf{R0@0} \overset{\mathrm{reg}}{\longmapsto} x * \dots \text{(other resources)} \vdash \mathit{WP} \; \mathsf{Normal} \; @ \; 0 \; \left\{ \mathsf{m.m} = \mathsf{Halted} * \; \mathsf{R0@0} \overset{\mathrm{reg}}{\longmapsto} x + 2 \right\}$$

## 3.2 Proving the Specification

- 3.2.1 First Instruction. To safely execute the first instruction of VM0, mov R5 #p (where p is an immediate), we need, as captured in our SS-mov proof rule for an immediate-to-register mov, to know/show:

- (1) The value a of the program counter, which indicates the location of the current instruction in the memory, as captured by the points-to for registers  $pc@i \xrightarrow{reg} a$  (here,  $pc@0 \xrightarrow{reg} pp_0$ ).

- (2) Knowledge that the page at address a (here,  $pp_0$ ) is in the accessible set s of PageIDs...

- (3) ...that are mapped for the current VM, as captured by ownership of the page tables points-to assertion,  $\operatorname{Pgt}@i \xrightarrow{\operatorname{acc}} s$  (here,  $\operatorname{Pgt}@0 \xrightarrow{\operatorname{acc}} s$ ).

- (4) Ownership of the memory points-to resource for that memory location,  $a \stackrel{\text{mem}}{\longmapsto} w$  (here,  $pp_0 \stackrel{\text{mem}}{\longmapsto} w$ ), which contains a word w that is the encoding of an immediate-to-register mov instruction (here, mov R0 #p).

- (5) Ownership of the register points-to resource for the affected register (here, R5@0  $\stackrel{\text{reg}}{\longmapsto}$  -); we do not need to know what it contains (as signified by the use of -), but we must have the right to update it.

After the mov instruction, the VM does not lose control (so the switching bit is False), and the execution mode is still Normal. We get the updated resources back in our context; in particular, the program counter has been incremented,  $pc@0 \xrightarrow{reg} pp_0 + 1$ , and the register now contains the immediate, R5@0  $\xrightarrow{reg} p$ ; the page tables and the instruction have not been affected, so we get their assertions back unchanged.

The proof rule requires exactly the resources needed to safely execute the instruction; other resources are implicitly kept unchanged via framing, which is a key feature of separation logic that saves us from maintaining global resources all the time, and helps keep the proof effort manageable.

```

SS-share

(1) ValidDesc(memtx, i, j, ps) \land (2)ps \subseteq s \land (3)hs \neq \emptyset \land IsHVC@i(s, a, Share) *

R1@i \xrightarrow{reg} l * R2@i \xrightarrow{reg} - * (4)Mb@i \xrightarrow{tx} ptx * (5)MemPage(ptx, memtx) *

(6) \bigstar (Pgt@p \stackrel{\text{own}}{\longmapsto} i * Pgt@<math>p \stackrel{\text{excl}}{\longmapsto} \text{True}) * (7) FreshHandles(hs)

SSWP \ \mathsf{Normal} \ @ \ i \ \begin{cases} \mathsf{pc}@i \overset{\mathsf{reg}}{\longmapsto} a + 1 * a \overset{\mathsf{mem}}{\longmapsto} \mathsf{hvc} * \mathsf{Pgt}@i \overset{\mathsf{acc}}{\longmapsto} s * \\ \mathsf{R0}@i \overset{\mathsf{reg}}{\longmapsto} \mathsf{Succ} * \mathsf{R1}@i \overset{\mathsf{reg}}{\longmapsto} l * \\ \mathsf{Mb}@i \overset{\mathsf{tx}}{\longmapsto} \mathit{ptx} * \mathit{MemPage}(\mathit{ptx}, \mathit{memtx}) * \\ & \quad & \quad & \quad & \quad & \\ \mathsf{Pgt}@p \overset{\mathsf{own}}{\longmapsto} i * \mathsf{Pgt}@p \overset{\mathsf{excl}}{\longmapsto} \mathsf{False} * \\ & \quad & \quad & \quad & \\ \mathsf{p} \in \mathit{ps} \end{cases} \\ & \quad & \quad & \quad & \quad & \\ \exists h. \ h \in \mathit{hs} \land \mathsf{R2}@i \overset{\mathsf{reg}}{\longmapsto} h * \mathit{FreshHandles}(\mathit{hs} \setminus \{\mathit{h}\}) * \\ & \quad & \quad & \quad & \\ \mathsf{Tran}@h \overset{\mathsf{tran}}{\longmapsto} (\mathit{i}, \mathit{j}, \mathit{ps}, \mathsf{Share}) * \mathsf{Tran}@h \overset{\mathsf{rtrv}}{\longmapsto} \mathsf{False} \end{cases}

SS-run

(1)i \neq 0 \land IsHVC@0(s, a, Run) * R1@0 \stackrel{\text{reg}}{\longmapsto} i * (2)RC_{1/2}@i \{\Psi_i\} * (3)RC_1@0 \{-\} *

\frac{ \text{(4)} \left( \left( \begin{array}{c} \operatorname{pc@0} \stackrel{\operatorname{reg}}{\longmapsto} a + 1 * a \stackrel{\operatorname{mem}}{\longmapsto} \operatorname{hvc} * \operatorname{Pgt@0} \stackrel{\operatorname{acc}}{\longmapsto} s * \\ \operatorname{R0@0} \stackrel{\operatorname{reg}}{\longmapsto} \operatorname{Run} * \operatorname{R1@0} \stackrel{\operatorname{reg}}{\longmapsto} i * \Phi_{othr} * \operatorname{RC}_1 @ 0 \left\{ \Psi_0 \right\} \right) - * \Psi_i * \Phi_{rest} \right) * \text{(5)} \Phi_{othr}}{SSWP \operatorname{Normal} @ 0 \left\{ (\operatorname{True}, \operatorname{Normal}) . \operatorname{RC}_{1/2} @ 0 \left\{ \Psi_0 \right\} * \Phi_{rest} \right\} }

WP-SSWP

WP \text{ m } @ i \text{ } \{\Phi\} \dashv \vdash SSWP \text{ m } @ i \text{ } \{(b, m'). ((b \land RCHolds@i) \lor (\neg b)) \twoheadrightarrow WP_{\mathcal{E}} \text{ m'} @ i \text{ } \{\Phi\}\}

RC-hold

RCHolds@i * RC_{1/2}@i \{\Psi\} \vdash \triangleright \Psi * RC_1@i \{\Psi\}

```

Fig. 6. Selected rules of VMSL

The SS-MOV rule, and all other single-instruction proof rules, use *SSWP*, our single-step variant of weakest preconditions. A *single-step weakest precondition* captures an intuitive idea (see §5): it is like a weakest precondition that only specifies the behaviour of a single step (an instruction). Applying a single-step weakest precondition takes resources specified in the premise, and returns resources stated in the postcondition, with the resulting execution mode and a bit indicating whether the instruction would cause the VM to lose control of the machine (the hypervisor switching to another VM to execute). Single-step weakest preconditions allow us to reason about one instruction at a time. We show how to formally apply it to *weakest precondition* in Section 3.3.

3.2.2 Sharing. The following instructions prepare the descriptor and arguments for the Share HVC at line 13. They only involve register manipulations, which can be reasoned about in a similar way to the first instruction, and memory accesses. To reason about memory access instructions,

including ldr and str, we need memory points-to predicates, with side conditions checking whether the VM has the permission to access the address, similar to (2) of SS-MOV.

Before reasoning about this specific Share, let us first consider the expected behaviour of a general Share HVC, specified by the SS-SHARE rule. To share pages represented by a set of PageIDs ps, VMi invokes a Share HVC with a descriptor in its TX page describing information about the transaction. Therefore, the proof rule requires (4) the TX page ptx; (5) ownership of the page with content memtx, which is expressed as memory points-tos for all locations of the page, connected by \*; and (1) knowledge that the descriptor stored in memtx is valid. In addition, after validating the descriptor, the page table is examined to check whether VMi is allowed to share those pages in ps. Therefore, the rule requires (6) page ownership  $\operatorname{Pgt}(p) \xrightarrow{\operatorname{own}} i$  and exclusiveness  $\operatorname{Pgt}(p) \xrightarrow{\operatorname{excl}} \operatorname{True}$ to VMi of each page p in ps. The side condition (2) plus the resource for page access (included in IsHVC) further ensure that VMi has access to those pages. This information, combined, ensures that VMi is allowed to share pages ps. To initiate a transaction, the hypervisor has to allocate a fresh transaction handle h, which is ensured by (7) remembering the set hs of available handles, and (3) requiring hs not be empty. The hypervisor further binds h to the meta-information and the state of the transaction that are also represented as resources, as in the postcondition. It is worth-noting that in practice a predicate can be built upon these resources, e.g. TranHandles shown in Section 4, leveraging the resource separation to guarantee that fresh and allocated handles are disjoint, which would reduce the handle availability reasoning to easy-to-discharge set disjointness side goals.

In our example, VM0 shares a single page p to VM1, so we let i, j, and ps be 0, 1, and  $\{p\}$  respectively. (1) is justified by the previous instructions constructing the descriptor correctly. (2) is justified as we assumed s to be  $\{pp_0; p; p_{tx}\}$ . (3) is justified by assuming a non-empty hs in the specification. After applying the proof rule, we get  $\operatorname{Tran}@h \stackrel{\operatorname{tran}}{\longmapsto} (0, 1, p, \operatorname{Share})$  and  $\operatorname{Tran}@h \stackrel{\operatorname{rtrv}}{\longmapsto} \operatorname{False}$ , stating that the requested transaction has been initiated, and is bound to h, which is also returned to VM0 so that it can refer to the transaction.

- 3.2.3 Messaging. To retrieve access to the shared page p, VM1 has to refer to the transaction with the handle h. To let VM1 do so, VM0 passes h to it by messaging at lines 14–21. Messaging essentially copies from the sender's TX page and pastes into the receiver's RX page; therefore, the proof rule for messaging requires the resources for the two pages and associated memory. We capture the state of VM1's RX page with a resource RXState@1  $\mapsto$  Some(1,0) in the example, expressing that VM0 has passed one word to VM1.

- 3.2.4 Scheduling. At line 29, VM0 runs VM1 to allow VM1 to receive the handle and retrieve page p. To reason about such scheduling, we introduce a resumption condition for VM1. A resumption condition for a VMi, denoted as  $RC_1@i$  { $\Psi$ }, captures the resources  $\Psi$  that need to be handed over to VMi to resume its execution. We use resumption conditions to express communication protocols (reminiscent of session types [Honda et al. 2011; Yoshida and Gheri 2020]) between VMs, and to transfer resources between VMs along the scheduling control flow. Accordingly, the proof rule for Run, SS-Run, uses a resumption condition. Concretely, we have to show the following to apply SS-Run when the primary VM, VM0, is about to run VMi:

- (1) The VM being run is not the primary VM itself.

- (2) VM0 has to satisfy the *resumption condition* of VMi,  $\Psi_i$ . The fraction  $^{1}/_{2}$  indicates that the *resumption condition* is split into two halves, and only one half is required. We elaborate on this point later.

- (3) We may pick the *resumption condition* of VM0,  $\Psi_0$ , that VM*i* will have to satisfy to yield back.

- (4) The magic wand P Q is separation logic's resource-aware implication. It is used here to express that with resources required by the rule (the first line) and (5), we can show  $\Psi_i$ , intuitively

the resources transferred to VM*i*, and the left over  $\Phi_{rest}$ , i.e. the resources that are required by the rule, but not needed to show  $\Psi_i$ , that are still owned by VM0 afterwards.

(5) Other resources required to justify  $\Psi_i$ .

By picking the right  $\Psi_i$  and  $\Psi_0$ , we describe the protocol according to which shared resources are transferred between the VMs. In our example, we know that to run VM1, VM0 has to have written x to the page p, shared the page, sent the handle, and run VM1. We express this in  $\Psi_i$  as follows:

$$\begin{split} \Psi_i &\stackrel{\text{def}}{=} p \stackrel{\text{mem}}{\longmapsto} x * \mathsf{Tran}@h \stackrel{\text{tran}}{\longmapsto} (0,1,\{p\},\mathsf{Share}) * \mathsf{Tran}@h \stackrel{\text{rtrv}}{\longmapsto} \mathsf{False} * \mathsf{Mb@1} \stackrel{\text{rx}}{\longmapsto} prx * \\ \mathsf{RXState@1} &\mapsto \mathsf{Some}(1,0) * prx \stackrel{\text{mem}}{\longmapsto} h * \mathsf{R0@0} \stackrel{\text{reg}}{\longmapsto} \mathsf{Run} * \mathsf{R1@0} \stackrel{\text{reg}}{\longmapsto} 1 * RC_{1/2}@0 \, \{\Psi_0\} \end{split}$$

Note that when VM1 yields back control to VM0, it needs to have established VM0's resumption condition, so we also include  $RC_{1/2}@0$  { $\Psi_0$ } in  $\Psi_i$ . VM1 thus can refer to  $\Psi_0$  and show it when yielding. In our example, we want to show that VM1 has incremented x by 2 and yielded. We express this in  $\Psi_0$ :

$$\Psi_0 \stackrel{\mathrm{def}}{=} p \stackrel{\mathrm{mem}}{\longmapsto} x + 2 * \mathsf{R0@0} \stackrel{\mathrm{reg}}{\longmapsto} \mathsf{Yield} * \mathsf{R1@0} \stackrel{\mathrm{reg}}{\longmapsto} 1$$

To justify (4), we let  $\Phi_{othr}$  be  $\Psi_i$  except for its last three assertions, and  $\Phi_{rest}$  naturally be the resources that are in the premise but not required by  $\Psi_i$ .

We get  $\Phi_{rest}$  and  $RC_{1/2}@0$  { $\Psi_0$ } after applying the rule. To explain how to get resources stated in  $\Psi_0$  out, we first introduce RCHolds@i. It assumes the resumption of VMi and can interact with the resumption condition of VMi by RC-hold. Intuitively speaking, the rule says that if we know the resumption condition of a VM, and the VM is indeed resumed, then the condition holds.  $\triangleright \Psi$  means that  $\Psi$  holds later, i.e. after taking a step in the underlying model (this is used to break circularity of definitions [Jung et al. 2016, 2015]). Back to the example, we already get  $RC_{1/2}@0$  { $\Psi_0$ } in the postcondition, so we would be able to apply this rule and proceed with the proof with the transferred-back resources in  $\Psi_0$  if we have RCHolds@0 as well. For now, readers only need to know that we can actually get it for free, because we have baked it into the definition of weakest preconditions in a way that we can get it out when a switching just happened.

3.2.5 Halting and Suspension. After loading the word x+2 at p to R0, the execution of VM0 is terminated by a halt. The proof rule updates the execution mode from Normal to Halted, and thus we obtain the postcondition of our initial specification,  $m = \text{Halted} \land \text{R0@0} \xrightarrow{\text{reg}} x+2$ , and conclude the proof.

The proof of VM0 does not consider the code of VM1, due to the 'VM-modularity' of VMSL. All we needed was an abstract characterisation of the protocol governing the interaction between VM0 and VM1, as captured by the resumption conditions.

The proof of VM1 is similarly done without considering the code of VM0, but concludes in a different way, as VM1 does not terminate, but instead suspends via the Yield at line 18. Because our protocol specifies it will not be scheduled again, it suffices to show that when we resume it, we get an immediate contradiction.

# 3.3 More on Single-step Weakest Preconditions and Resumption Conditions

The example above shows how single-step weakest preconditions and resumption conditions are the two key components that make reasoning with VMSL manageable. We now discuss them in more detail, and point out how an expressive higher-order separation logic like Iris makes reasoning sound and tractable.

*3.3.1 Single-step Weakest Preconditions.* Single-step weakest preconditions allow us to reason about a single instruction at a time. Rule WP-SSWP shows the relation between weakest preconditions

and single-step weakest preconditions: informally, it says that (setting aside the antecedent of the separating implication in the postcondition) to reason about a list of instructions, we can reason about the first one, and then the rest. This gives us, for our assembly language, the type of sequential composition we expect from higher-level languages. We can always apply WP-SSWP to transform a goal formulated in terms of weakest precondition into one formulated in terms of single-step weakest precondition, so that we can apply proof rules for individual instructions, and then proceed with the reasoning of the remaining instructions.

3.3.2 Resumption Conditions. We achieve modular reasoning between VMs through resumption conditions, which provide a form of rely-guarantee reasoning tailored for cooperative multitasking between VMs. To ensure that the entire logic integrates with resumption conditions, we bake RCHolds into the definition of weakest preconditions, so that we have to prove RCHolds when relinquishing control, and in exchange we can assume it when getting control back (as in the postcondition of WP-SSWP). This allows us to write specifications for individual VMs, and prove them separately without having to reason about other VMs' private state, and only having to reason about the private resources of the current VM and the shared resources that are transferred according to the communication upon scheduling. If a yielding (or scheduling) just happened, we immediately get to assume RCHolds, and we can obtain ownerships of the transferred resources stated in the resumption condition by RC-hold to continue the reasoning.

Then, to combine the proofs of the local specifications, we have to make sure that the resumption conditions are consistent and compatible, i.e. combined together, they form a unified global protocol, and therefore the combined global specification is valid. To do so, we use the fractional permissions of separation logic [Bornat et al. 2005; Boyland 2003]: we split the *RC* of a secondary VM in two halves, and let the primary VM and that secondary VM own one half each. Owning half is enough for both VMs, since SS-Run requires merely half to run the secondary, and RC-hold requires merely half to obtain ownership of the resources in the *RC*. In the example above, the protocol is specified by the *RC* of VM1 with the *RC* of VM0 embedded into it. The *RC* of VM1 is split into two fractions owned by the two VMs so that they conform to the same protocol.

Many concurrent separation logics, including Iris, already define a standard mechanism to reason about concurrent programs: invariants. However, resumption conditions are more convenient for the scenarios we consider, as they only require the user to consider interference from other VMs when it occurs, namely at the point of yielding; invariants would force us to consider it (and show that it is not present) at every step of the program. Iris also defines 'non-atomic' invariants, which are a closer fit for our scenarios, as they can group multiple execution steps as a single critical section when holding an exclusive token. However, they do not address the issue completely: a sharing mechanism like invariants is still required to transfer those exclusive token between VMs.

Recursive Resumption Conditions. We have shown in the example above how we can embed one resumption condition into another to construct a run-and-yield protocol between two VMs. In fact, our logic more generally supports recursively defined resumption conditions, which are useful for reasoning about examples where the number of switchings is unknown or unbounded. Consider a 'ping-pong' example, in which a primary VM and a secondary VMi just keep running each other; we can model this protocol as follows:

$$\Psi_i \overset{\mathrm{def}}{=} \mathsf{R0@0} \overset{\mathrm{reg}}{\longmapsto} \mathsf{Run} * \mathsf{R1@0} \overset{\mathrm{reg}}{\longmapsto} i * \mathit{RC}_{^{1/2}} @0 \left\{ \mathsf{R0@0} \overset{\mathrm{reg}}{\longmapsto} \mathsf{Yield} * \mathsf{R1@0} \overset{\mathrm{reg}}{\longmapsto} i * \mathit{RC}_{^{1/2}} @i \left\{ \Psi_i \right\} \right\}$$

The use of RC in  $\Psi_i$  ensures that  $\Psi_i$  is well-defined by the soundness of Iris higher-order ghost states and guarded recursion. Technically, RCs are defined using so-called saved propositions, which means that the recursive occurrence of  $\Psi_i$  is automatically guarded (even without an explicit 'later'

modality  $\triangleright$ ) and hence  $\Psi_i$  is well-defined. Using a logic with guarded recursion like Iris means we do not need to be concerned about soundness of these definitions, as one would have to be if working directly over the operational semantics.

3.3.3 Formalising in Iris. We formalise VMSL using Iris because it allows us to capture and generalize the well-established ideas behind the two logical constructs. We use Iris's primitives and leverage its advanced features, such as higher-order ghost states and guarded recursion, as demonstrated in the recursive example above. The resulting solution is sound and compatible with existing Iris logical constructs thanks to our foundational approach. We use the combination of resumption conditions and invariants in Section 4, and believe such compatibility would also be useful to tackle for example interrupts and proper concurrency. Moreover, our solution is language/model-agnostic, therefore can be instantiated with different low-level languages and used to the reasoning of them – e.g., VMSL is obtained by instantiating it with the HVC model.

## 4 REASONING IN THE PRESENCE OF UNKNOWN VMS

In our full motivating example in Figure 1, VM0 runs an unknown VM2 before running VM1 to let it retrieve the shared page. We assume that page  $pp_2$ , a page that VM0 and VM1 have no access to, is the only page that VM2 has access to except for its mailbox pages. Since the hypervisor provides isolation between VMs, we would like to show that the effect of VM2 is contained, in the sense that it cannot interfere with the sharing of the page p, nor change its contents. We capture this by showing that the same specification holds for VM0 as in the previous section.

This kind of scenario underpins many use cases of the kind of thin hypervisor we are modelling. For instance, if a secondary VM running some safety-critical service only interacts with the primary VM (running the operating system for scheduling and simple memory sharing), then other VMs cannot manipulate or break the secondary VM through malicious writes to memory.

We leverage the basic memory integrity mechanism of the machine to show *robust safety* for some key scenarios, that is, safety even in the presence of interactions with arbitrary unknown VMs trying to violate memory isolation, including by making hypercalls to attempt to get access to the private memory of other VMs. There are two overall shapes of scenarios: (1) When the primary VM is safe, strong properties hold for the whole system. (2) When the primary VM is compromised, because the primary VM is where the scheduler resides, and because it therefore interacts with all the secondary VMs (at least for scheduling), these strong properties do not hold, but some weaker properties still hold for known secondary VMs.

Proving robust safety. Proving robust safety for a machine with only known VMs is straightforward, as the property is captured by VMSL: (1) For each known VM, we prove a weakest precondition. (2) We apply the adequacy theorem, which combines the proved weakest preconditions of all VMs together, to get a valid global execution of the whole machine. However, this approach does not work directly if an extra unknown VM is considered. To be able to apply the adequacy theorem, we first have to establish a weakest precondition for that unknown VM under conditions that are compatible with the resources used for the other VMs. Because we do not have a concrete program, we do not know whether the program will behave properly, or try to maliciously write to a memory cell that exclusively belongs to another VM, or share memory with other VMs via hypercalls, or any combination of these. Therefore, the questions we face are how to obtain a weakest precondition for an unknown VM, and whether we can use VMSL to establish one.

Inspired by models for capabilities [Devriese et al. 2016; Georges et al. 2022a; Swasey et al. 2017], our answer is that we can do so using logical relations. We define two logical relations that are compatible with each other, one for each of the two scenarios. We introduce the logical relation for

the first scenario and illustrate it on the example of Figure 1 in Section 4.1, and describe how the second logical relation is derived by extending the first in Section 4.2.

## 4.1 A Logical Relation for Unknown Secondary VMs

To prove examples like Figure 1, we define a unary logical relation  $\mathcal{R}$  whose fundamental theorem gives us a weakest precondition for any unknown secondary VMi. Our logical relation states that, given the state of the page table and in-flight transactions that determine which memory pages VMi has or may get access to, as defined by InterpAccess, the execution of VMi can be safely resumed, as defined by InterpExecute:

$$\mathcal{R}(i) \stackrel{\text{def}}{=} \mathit{InterpAccess}(i) \twoheadrightarrow \mathit{InterpExecute}(i)$$

Then, the *fundamental theorem of the logical relation* (*FTLR*) just states that the logical relation holds for any VMID *i* except for 0:

$$\forall i. i \neq 0 \rightarrow \mathcal{R}(i)$$

From the perspective of proving the *FTLR*, *InterpAccess* can be regarded as a predicate specifying the exact resources we need to prove the execution of VM*i*. We define *InterpExecute* in terms of a *weakest precondition* to capture that if the execution of the VM is resumed, with the resources needed to resume it, then we can execute the VM until it stops or suspends again:

$$InterpExecute(i) \stackrel{\text{def}}{=} RCHolds@i * WP \text{ Normal } @ i \{ \top \}$$

It is sufficient for the postcondition to be  $\top$ , because we do not need to know what the state of the unknown VM is at the point of halting (in fact, we would not be able to specify it anyway).

4.1.1 Defining InterpAccess. During the execution, VMi may execute any valid instructions, and so we cannot make assumptions about the content of memory of VMi that would restrict its behaviours. Therefore, we have to reason about all possible cases of its execution in the proof of FTLR (which we do by using the proof rules of VMSL).

The definition of *InterpAccess* for a VM*i* follows two principles: (1) It must allow us to characterise the behaviour of VM*i* enough to prove our desired safety property, whatever instructions VM*i* executes. The way this manifests in the proof is that it must include enough resources for us to be able to apply our proof rules for any instructions. (2) It should not needlessly limit our ability to reason about other VMs. Giving to VM*i* resources that VM*j* could own means we might not have necessary resources to prove the specification of VM*j*. Therefore, *InterpAccess(i)* should contain just enough resources to reason about VM*i*. These two principles make *InterpAccess(i)* the footprint of running an arbitrary program on VM*i*. Figure 7 shows the top-level definition of *InterpAccess*.

In general, InterpAccess(i) is parametrised by  $s_{acc}$ , the set of pages that VMi has access to, and  $\tau$ , the map from Word to Transaction representing all in-flight transactions. Intuitively, the behaviour of VMi, in particular its interactions with other VMs, is (and can only be) restricted by information carried by these two variables. For instance, VMi cannot share a page whose PageID is not in  $s_{acc}$ , nor retrieve pages shared with another VM according to  $\tau$ . The main goals of InterpAccess is therefore to interpret these variables with resources, following the two principles above.

Among all the resources of InterpAccess(i), some are exclusively owned by VMi, and some have to be shared between VMi and other VMs due to the communication allowed by HVCs. The shared part is transferred from the primary to VMi upon resumption (via  $\Psi_i$ ) and is given back to the primary upon yielding (via  $\Psi_0$ ), using RCs.  $\Psi_i$  and  $\Psi_0$  are parametrised by an extra  $\tau'$ , to represent new transactions allocated or updated during the suspension of VMi. The connection between  $\tau$  and  $\tau'$  is captured by the relation  $\tau \sim \tau'$ , that is that, the transactions in which VMi is the sender or receiver in  $\tau$  cannot be touched by other VMs during its suspension, and therefore remain

```

InterpAccess(i) \stackrel{\text{def}}{=} \forall s_{acc}, \tau. \text{ (1)} Pgt@i \xrightarrow{\text{acc}} s_{acc} * \text{ (2)} PgtOea(s_{oea}) * \\ (3) MemPages(s_{oea} \cup excl\_pages(\tau)) * \text{ (4)} PgtTranP(\tau) * \text{ (5)} RC_{1/2}@i \{\Psi_i\} * \dots \\ \Psi_i \stackrel{\text{def}}{=} \exists \tau'. \tau \sim \tau' \land \text{ (6)} TranHandles(\tau') * \text{ (7)} PgtTranS(\tau') * \\ (8) MemPages(shared\_pages(\tau')) * \text{ (9)} RC_{1/2}@0 \{\Psi_0\} * \dots

```

Fig. 7. The shape of the definition of InterpAccess(i). All predicates are implicitly parametrised by i if i is mentioned in their definitions. We refer readers to the Coq formalisation for the full definition.

unchanged in  $\tau'$ . This relation allows us to unify the two, safely replacing  $\tau$  with  $\tau'$ . We then only work with  $\tau'$ , which includes all ongoing transactions when VMi is actually executed.

We present this definition by first considering the resources interpreting  $s_{acc}$  and  $\tau'$  as a whole, without distinguishing between exclusively owned and shared, to argue why the unknown VM needs them, and later argue why and how to divide them into owned and shared portions.

4.1.2 Interpreting  $s_{acc}$ . The interpretation of  $s_{acc}$  is split as follows: First, (1) states that these pages are accessible to VMi, which is required by all the proof rules (e.g. (3) of SS-MOV). Second, (2) provides page table resources for pages that VMi owns and has exclusive access to (denoted as  $s_{oea}$  and computed from  $s_{acc}$  and  $\tau$ ), which is defined as  $*_{p \in s_{oea}} \operatorname{Pgt}@p \xrightarrow{\operatorname{own}} i * \operatorname{Pgt}@p \xrightarrow{\operatorname{excl}} \operatorname{True}$  (or  $\operatorname{PgtOE}(s_{oea}, i, \operatorname{True})$  in short). Those resources are required by the proof rules (e.g. (6) of SS-SHARE) if VMi shares pages that are in  $s_{oea}$ .

These two components are exclusively owned by VMi since no other VMs may require them. Another necessary but partially shared component is the memory of  $s_{acc}$ ,  $MemPages(s_{acc})$ , which is required by rules for memory access instructions. We divide  $s_{acc}$  (and the predicate correspondingly) in two parts: memory pages that VMi has exclusive access to, and the remainder that is shared with other VMs. The former is captured by  $s_{oea}$  plus pages that are lent to VMi, collected by  $excl\_pages(\tau')$ , as in (3); the latter is collected by  $shared\_pages(\tau')$  as in (7).

4.1.3 Interpreting t'. In general, three kinds of resources could be necessary to allow VMi to perform memory sharing HVCs on t: Tran@ $h \stackrel{\text{tran}}{\longmapsto} t$ .meta is necessary to refer to t for any sharing HVCs; Tran@ $h \stackrel{\text{rtrv}}{\longmapsto} t$ .retri is necessary to retrieve the access to shared pages t.pgs; and  $PgtOE(t,pgs,\_,\_)$  is necessary to update the status of the shared pages.

These resources are split into fractions such that some are owned by VMi, and some are shared. The owned and shared fractions are used to interpret transactions of  $\tau$  and  $\tau'$  respectively, and unified later by  $\tau \sim \tau'$  (so they both interpret  $\tau'$ ). For instance, a points-to for transactions is split into three fractions that must agree on their values. One third in some cases is owned by VMi, and at least another one third is shared in all cases. The points-tos for the page table are split and unified in the same way, and the splitting is then lifted to PgtOE. At least two fractions of PgtOE that interpret t are shared, which allows us to derive the fact that pages shared by two transactions are disjoint by leveraging the exclusivity of  $PgtOE_{2/3}$  that is derived from that of the underlying page table points-tos.

Now let us zoom in on several representative cases outlined in table 2 to see why those resources are distributed like this. In case "i, j, Share, False", VMi is the sender, and therefore the owner of the shared pages. All fractions of the three resources are required as the sender could Reclaim access, recycling the two transaction points-tos and updating PgtOE by the proof rule. The owned fractions allow VMi to remember that it has shared t.pgs even after a suspension. The receiver

Table 2. Select cases of how a transaction t is interpreted. Column one gives metadata and state of t, where j and k are VMIDs of two other VMs. Columns two to four give the required fractions of the three kinds of required resources.  $\frac{1}{3} + \frac{2}{3}$  under column two means  $\operatorname{Tran}@h \stackrel{\operatorname{tran}}{\longmapsto}_1 t$ . meta is required in total, with  $\frac{1}{3}$  of it owned by the unknown VMi, and  $\frac{2}{3}$  shared.

| t.sndr, t.rcvr, t.type, t.retri   | $\operatorname{Tran}@h \stackrel{\operatorname{tran}}{\longmapsto} t.\operatorname{meta}$ | $\operatorname{Tran}@h \stackrel{\operatorname{rtrv}}{\longmapsto} t.\operatorname{retri}$ | <i>PgtOE</i> ( <i>t</i> .pgs, _, _) |

|-----------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------|

| i, j, Share, False                | $\frac{1}{3} + \frac{2}{3}$                                                               | 1                                                                                          | $\frac{1}{3} + \frac{2}{3}$         |

| i, j, Donate, False               | 1                                                                                         | 1                                                                                          | 1                                   |

| <i>j</i> , <i>i</i> , Share, True | 2/3                                                                                       | $\frac{1}{2} + \frac{1}{2}$                                                                | 2/3                                 |

| <i>j</i> , <i>i</i> , Lend, True  | 2/3                                                                                       | $\frac{1}{2} + \frac{1}{2}$                                                                | 2/3                                 |

| j, k, _, _                        | 1/3                                                                                       | 0                                                                                          | 2/3                                 |

doesn't need them to Retrieve or Relinquish. In case "i, j, Donate, False", all resources are shared, as the receiver could Retrieve, which gives it ownership of the pages t.pgs. In case "j, i, Lend, True", VMi as the receiver does not own page table resources nor the points-tos for transaction, as there is no way for it to get ownership of those pages (and full ownership of the three resources is not required by the proof rules of Retrieve or Relinquish). However, it owns half of the retrieval points-to, so that it can remember the fact that it has retrieved after a suspension. In the last case "i, k,  $\_$ ,  $\_$ ", VMi is neither the sender nor the receiver (which is the case of VM2 in our example), only the minimum amount of resources is required (in our example, Tran@ $h \stackrel{\text{tran}}{\longmapsto} {}_{1/3} (0, 1, \{p\}, \text{Share})$  and  $\text{Pgt}@p \stackrel{\text{own}}{\longmapsto} 0 * \text{Pgt}@p \stackrel{\text{excl}}{\longmapsto} \text{False}$ ).

Resources specified in Table 2 are distributed in (4), (6), and (7). (6) includes the least amount of fractions required by all cases, i.e. 1/3, 0, and 2/3, of the three kinds of resources respectively, for each transaction in  $\tau'$ :

Remaining owned and shared fractions are distributed in (4) and (7) respectively with definitions of similar shapes as (6).

4.1.4 General Protocols. (9) in Figure 7 is one half of the resumption condition specifying which resources are supposed to be returned back to the primary VM to resume its execution. Generally speaking, the same resources transferred to VMi are passed back, plus the recursive resumption condition of VMi which allows the primary to run VMi multiple times.

$$\Psi_0 \overset{def}{=} \exists \tau. \textit{TranHandles}(\tau) * \textit{PgtTranS}(\tau) * \textit{MemPages}(\textit{shared\_pages}(\tau)) * \ldots * \textit{RC}_{1/2} @i \{\Psi_i\}$$

We call such a protocol specified by the two resumption conditions the *general protocol* of VMi. It is general in the sense that it specifies necessary resources to support arbitrary execution of VMi, for arbitrary numbers of resumptions, and it is used to reason about unknown VMs. In the case where the primary VM is unknown, we sometimes need an additional mechanism for reasoning about sharing between communicating VMs, see the example considered in Section 4.2.

- 4.1.5 Proving the FTLR. To show that the FTLR holds, we have to consider all possible instructions since the program of the VM is unknown. For each instruction, we apply the corresponding general proof rule of VMSL. See the Coq formalisation for the proof.

- 4.1.6 *Instantiating the FTLR.* We now demonstrate how we use the logical relation to reason about the full motivating example by instantiating the *FTLR*. Recall that our approach is to (1) show a

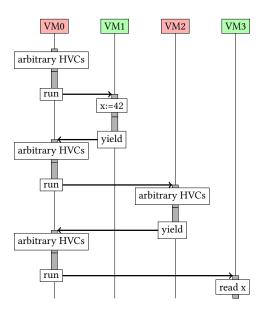

Fig. 8. A compromised primary VM is also contained: memory integrity (illustrating defensive code). This assumes VM1 and VM3 initially exclusively share a page p containing location x.

weakest precondition for each of the three VMs, assuming resources describing the initial state of the machine; and (2) combine them to apply the adequacy theorem, which provides these resources.

The weakest precondition for VM1 can be proved as for the simplified example. To show the weakest precondition for VM2, we instantiate the *FTLR* with *VMID* 2. We then have to pick proper  $s_{acc}$  and  $\tau$  such that the required resources are disjoint and consistent with resources required by the other two known VMs. That is, all initial resources are exclusively owned by one VM, and the protocols specified in resumption conditions agree with each other. We let  $\tau$  be  $\emptyset$ , since at the beginning there are no transactions, and we let  $s_{acc}$  be  $\{p_{tx2}; p_{rx2}; pp_2\}$ . To show the weakest precondition for VM0, which now runs VM2 before VM1, we have to show the resumption condition of VM2 specified in *InterpAccess*(2). In particular, we let  $\tau'$  be  $\{h \mapsto (0, 1, \{p\}, Share, False)\}$ , whose interpretation in *TranHandles* will disallow any malicious HVCs, such as retrieving access to p, by VM2. The same resources are included in  $\Psi_0$  and given back, so this transfer does not affect the reasoning about the two known VMs after running VM2.

4.1.7 Capturing Safety. The fact that we are able to prove (using our logical relation) that VM0 and VM1 can safely share a page, even though VM2 runs in between and gets the opportunity to try to interfere, shows that our underlying machine-with-HVCs model is *secure*, in the sense that executing those HVCs will not break isolation unintentionally.

## 4.2 A Logical Relation for Unknown Primary VMs

We have shown how to reason in the presence of unknown secondary VMs using our first logical relation. However, secondary VMs also get some guarantees when the primary VM is unknown (and possibly compromised). For example, consider the scenario in Figure 8: only two secondary VMs, VM1 and VM3, are known, and a page p with 42 stored in it is shared between them. We would like to show that VM3 can read that same value from the page, even with the unknown primary

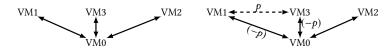

Fig. 9. An illustration of how resources are shared among VMs in Figure 8. Regular arrows represent the resources of the general protocol, where (-p) means the resources of page p are excluded. Instead, those resources are shared via an invariant represented as the dashed arrow.

VM0 in addition to the unknown secondary VM2. In this example, as before, we can instantiate the *FTLR* to get a weakest precondition for VM2, but we cannot do the same for VM0.

To deal with scenarios with an unknown primary VM, we develop a second logical relation, whose *FTLR* gives a weakest precondition for the primary VM. We ensure that this second logical relation is also compatible with our previous logical relation. This enables us to show safety of scenarios with both arbitrary unknown primary and secondary VMs, including the example above. In such scenarios, programs of known secondaries have to be written defensively, as they may be scheduled at any point. In this section, we show how we design and use this second logical relation, and refer the reader to the Coq formalisation for the full definition.

The statement of the *FTLR* of the new logical relation is symmetrical to the previous one: we now require i to be 0. As before, *InterpExecute* is defined as just WP 0 @ Normal  $\{\top\}$ , and moreover *RCHolds* is not needed as we always run the primary first. The difference is in *InterpAccess*, which generalises the former to support running arbitrary secondary VMs, namely the extra power of the primary VM. From the perspective of resources, the new *InterpAccess* includes (1) resources that supports VM0's execution except for running other VMs, which is identical to what is required by a secondary VM as in Section 4.1.1; and (2) resources required by resumption conditions of all secondary VMs to support running these VMs, which is basically their resumption conditions plus the union of resources required by them.

The crux of defining the new *InterpAccess* is specifying *all* the resumption conditions, i.e. protocols between all secondaries and the primary. For unknown secondaries, as shown in the previous subsection, we can use the general protocol. For known secondaries, because we want our FTLR to be generic in their code, the protocol cannot depend on their code (so, here, we cannot take the approach we used for the example in Figure 1). Moreover, we cannot use the general protocol for known code either, as it is too general to be used to prove e.g. the example in Figure 8. The technical problem arises from: (1) the very loose assumption on the content of memory, which is quantified over existentially in the general protocol. That is, we want to show the shared page p contains a specific number, but the general protocol only gives us that there is some number in p. (2) the fact that resumption conditions only allow transferring resources along the scheduling control flow via the primary VM (as illustrated on the left of Figure 9). With the cooperative scheduling mechanism we model, secondary VMs can only yield to the primary VM, not directly from one secondary VM to another. This means that in this example, the shared page p can only be transferred between VM1 and VM3 with VM0 as a middleperson.

4.2.1 Our Approach. Instead, we exclude the page p from the general protocol, and share it between VM1 and VM3 in another way (which we can do since p is not accessible to VM0). To do this, we use invariants as a complementary resource sharing mechanism, for resources that cannot or should not be shared via the general protocol. In this example, assuming p's value is always 42 after VM1 writes to it, we can establish a trivial invariant, as illustrated in Figure 9, with the memory resources of page p.

How We Implement Our Approach. Recall that the general protocol specifies the resources a secondary shares with all other VMs, although they are only ever transferred via the primary. It indicates that it is safe to run an unknown primary without resources that secondaries shared with other secondaries in the general protocol. We therefore can divide the resources of the general protocol into slices, one for each pair of VMIDs, which only contain one-to-one shared resources. This way, we can now safely remove secondary-to-secondary slices from the general protocol between a secondary and the primary. We then parametrise the logical relation by the secondary-tosecondary slices, thereby allowing the user of the FTLR to decide which of those slices are (partially) transferred via the unknown primary. For instance, resources that VM1 shares using its general protocol are divided into three slices containing resources that it shares with (1) VM0; (2) VM2; and (3) VM3. We say the slice from VM1 to VM2 is full if it contains all related resources required by the general protocol between VM1 and the primary. We then instantiate the FTLR with full slices (1) and (2), and (3) minus the memory of page p, to exclude that page from the VM1-to-VM3 slice. By doing so, yielding of VM1 will not require the resources for page p, and therefore we can use it to establish the invariant. Moreover, by letting slices from VM2 to other VMs be full, we can actually recover the general protocol of VM2, therefore making the two logical relations compatible.

## 5 RELATED WORK

Hypervisor and OS verification. There are several lines of work on hypervisor verification, including HASPOC [Baumann et al. 2016, 2019], SeKVM [Li et al. 2021a,b; Tao et al. 2021], Hyper-V [Leinenbach and Santen 2009], and seL4 [Klein et al. 2014, 2009].

The HASPOC project is aimed at designing a secure virtualisation platform for ARMv8, for which they prove information-flow security. They introduce an idealised model in which information-flow security holds by construction, and prove a bisimulation between it and the concrete platform model. In their model, each VM's memory is isolated and cannot be shared; instead, inter-VM communication is restricted to a messaging mechanism similar to the one we model.

The main focus of SeKVM is on hypervisor verification. As part of it, they capture generic isolation properties between virtual machines and their hypervisor (based on KVM) in the form of non-interference results about their combined model of the machine and the hypervisor, capturing both integrity and secrecy. They support memory sharing in a much more restrictive way, only allowing a VM to share encrypted data with the less privileged portion of the hypervisor to support I/O virtualization.

Microsoft's Hyper-V is an industrial hypervisor partially verified with the VCC verification suite [Cohen et al. 2009], and their verification effort focuses on low-level concurrent C code. Most of their verification effort relates the hypervisor implementation to its specification, but not on validating that top-level specification, nor on its security properties.

seL4 is a formally verified OS kernel. Whereas in our setting, scheduling is outsourced to a primary VM, in their setting, scheduling is done by seL4 itself. In addition to functional correctness, seL4 includes a proof of some non-interference properties [Murray et al. 2013], which they prove over the kernel specification. The integrity result for seL4 [Sewell et al. 2011] considers a small operating system that manages a set of capabilities with various authorities (write, read, send, receive, grant, etc.) over various objects. Their operating system corresponds to the combination of our hypervisor and a "receptive" primary that waits for requests, checks they are allowed, and executes them. In that setting, they consider what kind of capabilities are accessible through privilege escalation. This is similar to the way in which our logical relations have to consider what can be acquired transitively through transactions and memory.

These efforts primarily focus on verifying the implementation of system software (including APIs exposed to clients). Our work is complementary, in that our approach factors the integrity (but

not the secrecy) part of their security results into a logic to reason about concrete programs using hypercall APIs, and a logical relation that captures isolation. This, in contrast to their approaches, enables us to give specifications and verify individual concrete scenarios, whereas, in our terms, their results are concerned with composing exclusively unknown VMs.

In addition, these lines of work make drastic simplifying assumptions, as the actual behaviour of page tables, especially in the presence of concurrency, is only beginning to be understood precisely enough for verification [Simner et al. 2022]. Nonetheless, there is some work on hypervisor verification against authoritative models: Nienhuis et al. [Nienhuis et al. 2020] and Bauereiss et al. [Bauereiss et al. 2022] prove security properties above full-scale, authoritative, formal ISA models of the CHERI and Morello capability architectures. These properties are finer-grained than ours thanks to capabilities, but weaker in that they are architectural invariants, and thus cannot rely on properties of known code. Sammler et al. [Sammler et al. 2022] develop a separation logic above authoritative, formal ISA models of Arm-A and RISC-V by specialising the ISA definition to partially concrete opcodes through (unverified) symbolic evaluation [Armstrong et al. 2021]. They focus on verifying local specifications of known code, including some exception handlers.